Upotreba mikroprocesora ili digitalnih procesora signala u dizajnu različitih automatskih sistema omogućava stvaranje uređaja čija je posebnost u tome što ovdje postoje hardver i softver u obliku nedjeljivog hardversko-softverskog kompleksa. Proces razvoja takvog hardverskog i softverskog kompleksa prikladno je predstaviti kao niz od tri faze dizajna:

- 1. razvoj (i/ili izbor standardnog) hardvera;

- 2. razvoj aplikacija softver;

- 3. Integracija hardvera i softvera i debagovanje prototipa sistema.

Kada koristi mikroprocesor kao komponentu, programer sistema oslobađa se potrebe da dizajnira i podrži tehničkom dokumentacijom najsloženiji centralni dio proizvoda. Projektna dokumentacija za hardver proizvoda sadrži samo dokumentaciju za hardver za interfejs mikroprocesora sa senzorima i aktuatorima kontrolnog objekta. Pojavom analognih (signalnih) mikroprocesora, integriranih DAC-a i ADC-a, te raznih velikih integriranih kola (LSI) specijalizovanih kontrolera, sve složeniji funkcionalni dijelovi automatskog sistema prelaze iz kategorije podsistema u kategoriju sastavnih elemenata. Budući da su ovi sastavni elementi složeno organizirani uređaji koji rade pod programskom kontrolom, udio aplikativnog softvera u mikroprocesorskim sistemima ima stalnu tendenciju povećanja, a udio hardvera - smanjenju.

Ako je zadatak već postavljen, tada je najintenzivnija i najsloženija (zbog bliske veze s područjem primjene budućeg programa) faza rada faza formiranja algoritma za rješavanje zadatka. To je zbog činjenice da ova faza praktički nije podložna formalizaciji i stoga se ne može automatizirati konvencionalnim sredstvima. Projektni rad ovdje je duboko kreativan i u velikoj mjeri ovisi o iskustvu i kvalifikacijama programera.

Ilustrujmo gore navedeno jednim od mogućih pristupa kreiranju sistema pomoću mikroprocesora na primeru projektovanja digitalnog filtera.

Pretpostavimo da želite da kreirate niskopropusni filter prvog reda (LPF).

Na sl. 3.59, i prikazuje shematski dijagram takvog filtera. Redoslijed filtera je određen brojem reaktivnih elemenata uključenih u njega, tj. kondenzatori i induktori. Signali niske frekvencije proći kroz niskopropusni filter do njegovog izlaza. Visokofrekventni signali su "kratko spojeni" kroz kondenzator na masu i ne pojavljuju se na izlazu filtera. Na sl. 3.59, b prikazuje amplitudno-frekvencijski odziv (AFC) ovog filtera. Granična frekvencija filtera (frekvencija prekida, frekvencija infleksije) logaritamskog frekventnog odziva je = 1/f (rad/sec), gdje je f = RC vremenska konstanta. Za predstavljanje frekvencije u hercima koristi se relacija uc = 2rf.

Rice. 3.59 Niskopropusni filter: a) dijagram kola; b) frekvencijski odziv

Zapišimo diferencijalnu jednačinu koja opisuje procese koji se dešavaju u niskopropusnom filteru prikazanom na Sl. 3.59, uzimajući u obzir to

i = C dUout/dt,

tada će jednačina izgledati ovako

digitalni diskretni mikroprocesor automatski

Razmotrimo vrijednosti ulaznog i izlaznog signala u diskretnim vremenima nDt, gdje je n = 0, 1, 2, ... i zamijenimo izvod konačnom razlikom

tada će (3.6) poprimiti oblik

Izvršimo sljedeće transformacije sa (3.7):

Kombinirajmo prva dva člana u (3.8) i izvadimo ih iz zagrada,

Pomjerimo drugi član (3.9) na desnu stranu jednakosti i podijelimo lijevu i desnu stranu rezultirajuće jednakosti sa (Dt+RC). Onda

Podijelimo brojilac i imenilac članova na desnoj strani (3.10) sa Dt:

Konačno, označavajući k1 kao k2,

Dobili smo

Nakon implementacije (3.12) u obliku programa za mikroprocesor i korištenjem kola na sl. 3.60 u Dt<< RC, получим цифровой фильтр нижних частот

Rice. 3.60 Digitalni filterski krug

Digitalni uređaji bazirani na mikroprocesorima imaju niz prednosti u odnosu na analogne. Navedimo neke od njih koristeći primjer digitalnog filtera o kojem smo gore govorili:

- 1. Neosjetljivost karakteristika filtera na širenje parametara njegovih elemenata, njihov vremenski i temperaturni drift.

- 2. Mala veličina i visoka pouzdanost filtera povezana sa upotrebom LSI.

- 3. Lakoća promjene parametara i karakteristika digitalnog filtera, koja se, kada se koristi mikroprocesor, vrši modifikacijom softvera ili tablica koeficijenata.

- 4. Mogućnost implementacije adaptivnih filtera, tj. filteri sa promjenom parametara tokom rada.

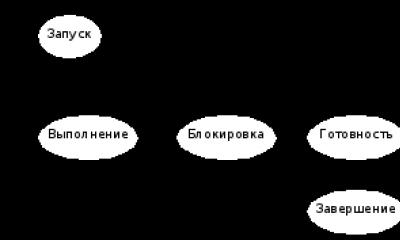

Proces projektovanja mikroprocesorskih sistema obuhvata tri faze (slika 1.1): 1) sistem; 2) dizajn funkcionalnog kola; 3) otklanjanje grešaka i evaluacija performansi.

Rice. 1.1. Faze projektovanja MPS-a

U fazi projektovanja sistema prvo se sprovodi sistemska analiza zadatka koji je dodeljen MPS-u, identifikuju se svrha, glavna svojstva, potrebe, ideje za implementaciju, iznos finansiranja i druge karakteristike dovoljne za donošenje odluke o putevima projektovanja. Zatim se formuliše funkcionalno ponašanje sistema i zahtevi za njim sa stanovišta obezbeđivanja skupa izvršenih funkcija, zahtevanih performansi, identifikacije kritičnih funkcija, određivanja sastava periferne opreme sistema, strukture ulaza i izlaza. podaci, karakteristike tokova podataka i kontrolne informacije. Razvija se prošireni algoritam za funkcionisanje sistema i formalizovani opis algoritma za rad MPS-a. Sledeći korak u fazi projektovanja sistema je određivanje broja nivoa MPS hijerarhije, veza između njih i spoljašnjeg okruženja ili sistema. Utvrđeni su zahtjevi za arhitekturom sistema, distribuirane funkcije implementirane od strane hardvera i softvera i opravdani zahtjevi za interfejs. Potrebno je uravnotežiti zahtjeve za hardverom i softverom sistema, uzimajući u obzir zadatu brzinu i mogućnost smanjenja složenosti i troškova, te smanjenje vremena razvoja. Što je više funkcija implementirano u hardveru, to su performanse veće, ali je arhitektura sistema složenija i vreme razvoja je duže.

Trenutno, zbog razvoja LSI i VLSI mogućnosti, postoji tendencija da se hardveru dodijele funkcije koje su se do nedavno obavljale samo u softveru. Integracija softverskih mogućnosti u dizajn hardvera, prvenstveno u obliku ROM firmvera ili "matematičkih" čipova, je oblast koja se sve više koristi u mikroprocesorskim sistemima. Mnoge funkcije operativnog sistema već počinju da se implementiraju u hardveru postavljanjem programa u ROM čipove. Možda će doći red na hardversku implementaciju funkcija programskog jezika.

Važna tačka u fazi projektovanja sistema je izbor elementarne baze, osnovnog MPC-a, tj. tip porodice mikroprocesora i drugi LSI. Na osnovu ove faze izrađuje se tehnička specifikacija (TOR).

Faza projektovanja sistema je uglavnom heuristička, a rezultat je blok dijagram mikroprocesorskog sistema i tehničke specifikacije, koje ukazuju na sve zahteve koje razvijeni MPS mora da zadovolji.

Faza funkcionalnog kola podijeljena je u tri područja: razvoj hardvera, razvoj softvera i razvoj pomoćnih alata, koji zauzvrat sadrže i hardverske i softverske dijelove. Karakteristike ove faze su sljedeće:

1) potreba za zajedničkim razvojem i otklanjanjem grešaka hardvera i softvera usmerenih na određenu strukturu hardvera;

2) korišćenje principijelno novih metoda i alata za razvoj i otklanjanje grešaka mikroprocesorskih sistema, kao što su emulatori unutar kola, analizatori logike i potpisa, kompleksi za otklanjanje grešaka i alati za automatizovano programiranje;

3) snažna međupovezanost i ravnomerna integracija faza projektovanja, u kojima programer istovremeno mora imati iskustvo u projektovanju mikroprocesorskih sistema, kao i da razume specifično područje njihove primene.

U fazi projektovanja funkcionalnog kola, na osnovu blok dijagrama MPS-a, razvijaju se funkcionalni i šematski dijagrami tehničkih sredstava, algoritama i aplikativnih programskih modula. Ovu fazu karakteriše široka upotreba standardnih kola i softverskih rješenja i snažna međuzavisnost hardvera i softvera, čiji se razvoj mora odvijati paralelno u svim fazama. Faza se završava integracijom hardvera i softvera, čime počinje faza otklanjanja grešaka cijelog MPS-a u cjelini.

Otklanjanje grešaka MPS-a je radno najintenzivnija faza, tako da razvoju ugrađenih kontrolnih alata i metoda za korišćenje standardnih alata za otklanjanje grešaka treba posvetiti istu pažnju kao i razvoju hardvera i softvera. Otklanjanje grešaka zahteva ugrađene alate, softver i hardver, kao i posebne uređaje kao što su analizatori logike i potpisa, kompleksi za otklanjanje grešaka i interni emulatori. Ugradnja dijagnostičkih i kontrolnih alata čini razvoj sistema nešto dužim i skupljim, ali uvelike olakšava njegovo otklanjanje grešaka i dalji rad.

Projektovanje sistema završava se pilot testiranjem razvijenog MPS-a u sistemu za koji je namenjen i procenom dobijenih karakteristika. Ukoliko rezultati ocjenjivanja ne zadovoljavaju zahtjeve tehničkih specifikacija, vrši se analiza uzroka i na osnovu nje se vrši redizajn pojedinih modula MPS-a ili cijelog sistema u cjelini.

Dizajn se završava izradom metodološke podrške koja sadrži preporuke za racionalno korišćenje projektovanog MPS-a i svu potrebnu dokumentaciju.

Razmatrane faze se po pravilu provode u obliku istraživačkog rada uz učešće relativno malog broja visokokvalifikovanih stručnjaka.

Dalje faze projektovanja obično se izvode u obliku razvojnih radova i zahtevaju uključivanje velikog broja izvođača.

Procesi automatizacije tehničke opreme preuzeli su najveći dio cjelokupne organizacije proizvodnje. Koriste se svuda u alatnim mašinama, mašinama i mehanizmima i robotskim sistemima. Nove tehnologije značajno povećavaju produktivnost rada, smanjujući uticaj ljudskog faktora na proizvodne rizike. Tehnički nivo i kvalitet proizvoda se također poboljšavaju. Mikroprocesorski sistemi su u svoje vrijeme bili inovativna tehnologija. Ali sada je to već uobičajeno, jer uređaji koji su napravljeni pomoću mikroprocesora imaju veće pokazatelje performansi u odnosu na uređaje napravljene na zasebnim logičkim kolima, uz ekonomske prednosti prvih.

Standardizacija procesa razvoja pojednostavljuje analizu i istraživanje u ovoj oblasti. To također čini jasnim trenutno stanje i moguće rezultate. Današnje kompanije za ugrađene mikroprocesorske sisteme koriste programibilna logička integrisana kola (FPGA) i kompjuterski potpomognute proizvodne sisteme za brzo, organizovano projektovanje. Koristeći FPGA, moguće je i otklanjanje grešaka i testiranje u realnom vremenu. Godišnje ažuriranje CAD-a omogućavaju vam da trošite sve manje vremena na monotoni i jednosložni rad, uz izbjegavanje očiglednih grešaka. Ovo vam omogućava da apstrahujete na više nivoe sistema i rešite teške probleme.

Proces razvoja ugrađenih mikroprocesorskih sistema može se predstaviti kao dva puta uzastopnih faza projektovanja. Prvi put je razvoj hardvera za ugrađeni mikroprocesorski sistem. Drugi put je dizajn softvera (slika 1).

Slika 1. Koraci dizajna

Ali nisu svi koraci rute potrebni. Modeliranje sistemskog hardvera se ne može vršiti tokom procesa razvoja. Stoga se neki koraci mogu eliminirati: priprema specifikacija modeliranja, generiranje modela, funkcionalno i vremensko modeliranje. Treba uzeti u obzir da modeliranje hardvera sistema povećava efikasnost procesa projektovanja u celini zbog ranijeg otkrivanja mogućih grešaka i njihovog otklanjanja.

Tipični koraci u dizajnu mikroprocesorskog sistema uključuju:

- Formalizacija različitih zahtjeva za sistem. Potrebno je izraditi eksterne specifikacije, tehničke specifikacije (TOR) za sistem, napomene o slici sistema od strane programera u dokumentaciji i navesti funkcije sistema.

- Razvoj strukture i arhitekture elemenata sistema. Potrebno je utvrditi interakciju između hardvera i softvera, funkcije periferije i softverske ljuske, odabrati mikroprocesorska rješenja na osnovu kojih će se sistem implementirati, te odrediti vremenske karakteristike.

- Razvoj i proizvodnja sistemskog hardvera i softvera. Potrebno je razviti strukturu i dijagrame kola, izraditi prototip i debagovati u osnovnim radnim uslovima. Razvoj softvera treba da se sastoji od algoritama, pisanja teksta izvornog programa, prevođenja izvornih programa u objektne programe, otklanjanja grešaka u softveru i simulacije.

- Opšte otklanjanje grešaka i testiranje prihvatljivosti u radnim uslovima.

Ljudski faktori dopuštaju neuspjeh i loše dizajnerske odluke. Postoje i hardverski kvarovi na uređajima. Na primjer, mogući su sljedeći izvori grešaka u koracima:

Faza 1. Logička nedosljednost zahtjeva, propusti, netačnosti algoritma.

Faza 2. Izostavljanje funkcija, izostavljanje nekih tokova informacija, nedosljednost protokola za interakciju između hardvera i programa, netačna definicija tehničkih zahtjeva, pogrešan izbor mikroprocesorskih rješenja, nepreciznosti algoritama.

Faza 3. Prilikom razvoja opreme - izostavljanje nekih funkcija, pogrešna interpretacija tehničkih specifikacija, nedostaci u krugovima sinhronizacije, kršenje pravila dizajna; pri razvoju softvera - propusti nekih funkcija tehničkih specifikacija, netačnosti u algoritmima, netačnosti u kodiranju; tokom proizvodnje prototipa - kvarovi komponenti i periferije, kvarovi u montaži i montaži.

Svaki od navedenih izvora greške može za sobom povući veliki broj fizičkih ili subjektivnih kvarova koji se moraju dalje identifikovati i otkloniti. Detekcija i lokalizacija kvara je komplikovana iz nekoliko razloga: prvo, može postojati više kvarova; drugo, monotonija simptoma raznih problema. Pošto ne postoje modeli subjektivnih grešaka, ovaj zadatak nije formalizovan. Rješenje je moguće korištenjem ekspertnih sistema - baze podataka sa postojećim problemima i njihovim rješenjima na osnovu praktičnog iskustva.

Subjektivni kvarovi se razlikuju od fizičkih po tome što se nakon detekcije, lokalizacije i korekcije više ne javljaju. Ali subjektivne greške mogu biti uvedene tokom razvoja specifikacije sistema, što znači da čak i nakon najtemeljnijeg testiranja sistema u odnosu na njegove specifikacije, i dalje može postojati subjektivna greška u sistemu.

Proces dizajna je iterativni proces, što znači da ako greške nisu u potpunosti eliminirane u jednoj fazi, one se mogu pojaviti u sljedećoj. Neophodno je otkriti greške što je prije moguće, potrebno je kontrolirati ispravnost projekta u svakoj fazi razvoja. Na primjer, kvarovi otkriveni u završnoj fazi prijema projekta mogu dovesti do korekcije specifikacija, a samim tim i do početka projektovanja cijelog sistema. Promjene u tehničkim specifikacijama dovode do istih posljedica (zbog potcjenjivanja i nedostatka informacija o sistemu).

Glavne metode za praćenje ispravnosti projektovanja su: verifikacija, modeliranje i testiranje.

Verifikacija vam omogućava da otkrijete ne samo trenutne greške, već i potencijalne greške koje se mogu pojaviti u budućim projektima koristeći blokove. Ali zahtijeva posebnu tehničku specifikaciju i relevantne vještine i pogodan je za velike projekte. Na malim projektima češće se koristi modeliranje ponašanja objekata i testiranje, jer ova opcija je isplativa i ne zahtijeva veliku količinu resursa.

Kontrola ispravnosti se postiže u svakoj fazi projektovanja potrebom da se izvrši modeliranje na različitim nivoima sistemskih apstrakcija i da se testiranjem provjeri ispravnost implementiranog dijela modela. Funkcionalna specifikacija se može simulirati i eksperimentalno testirati kako bi se odredio očekivani rezultat. Analizu također može obaviti tim stručnjaka. Nakon što je funkcionalna specifikacija odobrena, počinje razvoj funkcionalnih testova sistema, dizajniranih da utvrde ispravno funkcionisanje sistema u skladu sa njegovom funkcionalnom specifikacijom. Najefikasnije je razviti testove u potpunosti zasnovane na ovoj specifikaciji, jer to omogućava testiranje bilo koje implementacije sistema koja je sposobna da obavlja funkcije navedene u specifikaciji. Ova metoda je slična drugim, gdje se testovi grade u odnosu na specifične implementacije, ali preciznije uspoređuje očekivanja i rezultate razvoja.

Nakon što se otkrije greška, njen izvor mora biti lokalizovan kako bi se izvršila korekcija na odgovarajućem nivou apstraktne reprezentacije sistema i na odgovarajućem mestu. Netačna identifikacija izvora greške ili prilagođavanje na drugom nivou apstraktne reprezentacije sistema dovodi do toga da informacije o sistemu na najvišem nivou postaju pogrešne i ne mogu se koristiti za dalje otklanjanje grešaka tokom proizvodnje i rada sistema. .

Automatizacija monotonog rada razvoja testnih programa skraćuje period projektovanja i otklanjanja grešaka tako što se testovi dobijaju ranije (pošto se mogu generisati odmah nakon formiranja sistemskih zahteva) i omogućava dizajneru da menja specifikacije bez ponovnog pisanja svih testnih programa. U praksi je razvoj testa niži prioritet od projekta, pa se testni programi pojavljuju mnogo kasnije od njegovog završetka.

Dakle, uzimajući u obzir nijanse dizajna mikroprocesora, lako možete zaobići zamke tokom razvoja. Upotreba programabilnih logičkih integrisanih kola (FPGA) olakšava otklanjanje grešaka u neobjavljenoj seriji i omogućava vam da testirate dizajn i ispravite nedostatke. A sistemi za proizvodnju pomoću računara (CAD) pojednostavljuju razvoj, omogućavajući efikasniju preraspodjelu resursa.

Reference:

- SibGUTI [Elektronski izvor] / Dizajn mikroprocesora na FPGA – Način pristupa: http://ict.sibsutis.ru/sites/csc.sibsutis.ru/files/courses/mps/mp.pdf – besplatno. - kapa. sa ekrana. – jezik rus. (datum pristupa: 22. decembar 2017.).

- Zotov V. Embedded Development Kit - sistem dizajna za ugrađene mikroprocesorske sisteme zasnovane na FPGA serije FPGA iz Xilinxa. 2004. br. 3.

Kvalitativne i kvantitativne promjene u elementarnoj bazi kompjuterskog hardvera dovele su do promjene utvrđenih principa njihovog dizajna (kao što su kruta struktura, sekvencijalno centralno upravljanje, linearna organizacija memorije i nemogućnost prilagođavanja strukture računara karakteristikama računara). problem se rješava).

Klasični Von Neumann principi organizovanja računarskih sistema zamenjeni su idejama problemske orijentacije MPS-a, paralelne i cevovodne obrade informacija, upotrebe tabelarnih metoda obrade podataka, principa pravilnosti i homogenosti MPS struktura; Ideja stvaranja adaptivno rekonfigurabilnih sistema, kao i hardverske implementacije softverskih funkcija, postaje realna mogućnost. Stoga se trenutno pri projektovanju računarskih sistema zasnovanih na MPS-u primenjuje tzv. „3M“ princip: modularnost, umreženost, mikroprogramabilnost.

Princip modularne organizacije podrazumeva izgradnju računarskog i upravljačkog MPS-a na osnovu skupa modula: strukturno, funkcionalno i električni kompletnih računarskih uređaja koji omogućavaju rešavanje problema date klase samostalno ili u kombinaciji sa drugim modulima. Modularni pristup dizajnu mikroračunara i sistema omogućava (prilikom implementacije i univerzalnih i specijalizovanih modula) da se obezbedi stvaranje familija (serija) MPS-a, koji se razlikuju po funkcionalnosti i karakteristikama koje pokrivaju značajan spektar aplikacija, pomaže u smanjenju dizajna. troškove, a takođe pojednostavljuje povećanje snage i rekonfiguraciju sistema, odlaže zastarelost računarskih resursa.

Glavni metod razmjene informacija, za razliku od metode organiziranja proizvoljnih veza (po principu „svako sa svakim“), omogućava racionalizaciju i minimiziranje broja veza u MPS-u. Osigurava razmjenu informacija između funkcionalnih i strukturnih modula različitih nivoa koristeći autoputeve koji kombinuju ulazne i izlazne magistrale. Postoje jedno-, dvo-, trostruke i višelinijske veze. Neophodno je istaći međusobnu povezanost sklopovskih i strukturalnih rješenja koja se manifestiraju pri implementaciji ove metode razmjene u vidu stvaranja posebnih dvosmjernih bafer kaskada sa tri stabilna stanja i korištenjem vremenskog multipleksiranja kanala razmjene.

Mikroprogramsko upravljanje pruža najveću fleksibilnost u organizaciji multifunkcionalnih modula i omogućava problemsku orijentaciju MPS-a, kao i korištenje makro operacija u njima, što je efikasnije od korištenja standardnih potprograma. Osim toga, prijenos kontroliranih riječi u obliku šifriranih kodnih sekvenci ispunjava uslove za minimiziranje broja VLSI pinova i smanjenje broja interkonekcija u modulima.

Pored gore navedenih glavnih karakteristika dizajna MPS-a, treba istaći princip pravilnosti, koji pretpostavlja prirodnu ponovljivost elemenata strukture MPS-a i veza između njih. Primjena ovog principa omogućava povećanje integralne gustoće, smanjenje dužine spojeva na čipu, smanjenje vremena topološkog i sklopovskog projektiranja LSI i VLSI, te smanjenje broja sjecišta i tipova funkcionalnih i strukturnih elemenata.

Prilikom razvoja MPS arhitekture (faza sistema) potrebno je riješiti sljedeće zadatke:

Dati opis konceptualne strukture funkcionalnog ponašanja sistema sa stanovišta uzimanja u obzir interesa korisnika prilikom njegovog konstruisanja i organizovanja računarskog procesa u njemu;

Odrediti strukturu, nomenklaturu i karakteristike izrade softvera i firmver alata;

Opisati karakteristike interne organizacije tokova podataka i kontrolnih informacija;

Izvršiti analizu funkcionalne strukture i karakteristika fizičke implementacije sistemskih uređaja sa pozicije balansiranja softvera, firmvera i hardvera.

Glavne faze projektovanja MPS-a prikazane su na Sl. 3.1.

U početnoj fazi projektovanja, MPS se može opisati na jednom od sljedećih konceptualnih nivoa: „crna kutija“, strukturni, softverski, logički, sklop.

Na nivou “crne kutije”, MPS je opisan eksternim specifikacijama, koje navode eksterne karakteristike.

Rice. 3.1. Faze projektovanja MPS-a

Strukturni nivo kreiraju hardverske komponente MPS-a, što je opisano funkcijama pojedinih uređaja, njihovim međusobnim vezama i tokovima informacija.

Programski nivo je podijeljen na dva podnivoa (komande procesora i jezik), a MPS se tumači kao niz operatora ili naredbi koje izazivaju jednu ili drugu akciju na određenu strukturu podataka.

Logički nivo je svojstven isključivo diskretnim sistemima i podijeljen je na dva podnivoa: sklopna kola i prijenos registara. Prvi podnivo čine kapije (kombinacija kola i memorijskih elemenata) i operatori za obradu podataka izgrađeni na njihovoj osnovi. Drugi podnivo karakteriše viši stepen apstrakcije i predstavlja opis registara i prenosa podataka između njih. Sadrži dva dijela: informaciju i kontrolu: prvi formiraju registri, operatori i putevi prijenosa podataka, drugi daje vremenski zavisne signale koji iniciraju prijenos podataka između registara.

Nivo kola se zasniva na opisu rada diskretnih elemenata uređaja.

U životnom ciklusu MPS-a, kao i svakog diskretnog sistema, postoje tri faze: projektovanje, proizvodnja i rad. Svaka faza je podijeljena na nekoliko faza za koje postoje vjerovatnoće strukturalnih ili fizičkih kvarova. Kvarovi se dijele prema uzrocima: fizički, ako su uzrok defekti elemenata, i subjektivni, ako su uzrok greške u dizajnu.

Subjektivne greške se dijele na dizajn i interaktivne. Greške u dizajnu su uzrokovane nedostacima koji se unose u sistem u različitim fazama implementacije originalnog zadatka. Interaktivni kvarovi nastaju tokom rada zbog greške osoblja za održavanje (operatora). Posljedica kvara je greška, a jedan kvar može uzrokovati više grešaka, a istu grešku mogu uzrokovati mnoge kvarove.

Postoji i koncept defekta - fizička promjena parametara komponenti sistema koja prelazi prihvatljive granice. Defekti se nazivaju kvarovi ako su privremeni i kvarovi ako su trajni. Defekt se ne može otkriti sve dok se ne stvore uslovi da izazove kvar, čiji se rezultat mora, zauzvrat, prenijeti na izlaz objekta koji se proučava kako bi kvar bio vidljiv.

Dijagnoza greške je proces utvrđivanja uzroka greške na osnovu rezultata testiranja. Otklanjanje grešaka je proces otkrivanja grešaka i utvrđivanja izvora njihovog nastanka na osnovu rezultata testiranja prilikom projektovanja MPS-a. Alati za otklanjanje grešaka su uređaji, kompleksi i programi. Ponekad se otklanjanje grešaka odnosi na otkrivanje, lokalizaciju i eliminaciju grešaka. Uspješno otklanjanje grešaka ovisi o tome kako je sistem dizajniran, da li ima karakteristike koje olakšavaju otklanjanje grešaka i alate koji se koriste za otklanjanje grešaka. Da bi se izvršio otklanjanje grešaka, projektovani MPS mora imati svojstva upravljivosti, uočljivosti i predvidljivosti.

Upravljivost je svojstvo sistema u kojem se njegovo ponašanje može kontrolisati, tj. Moguće je zaustaviti funkcionisanje sistema u određenom stanju i ponovo pokrenuti sistem.

Uočljivost je svojstvo sistema koje omogućava praćenje ponašanja sistema i promene njegovih unutrašnjih stanja.

Predvidljivost je svojstvo sistema koje omogućava da se sistem uspostavi u stanju iz kojeg sva naredna stanja mogu biti predvidljiva.

MPS po svojoj složenosti, zahtjevima i funkcijama mogu se značajno razlikovati u radnim parametrima, količini softvera, vrsti mikroprocesorskog seta itd. U tom smislu, proces projektovanja može biti modifikovan u zavisnosti od zahteva za sistem. Na primjer, proces dizajniranja MPS-ova koji se međusobno razlikuju po sadržaju ROM-a sastojat će se od razvoja programa i proizvodnje ROM-ova. Prilikom projektovanja višeprocesorskih MPS-ova koji sadrže više tipova MPC-a, potrebno je rešiti pitanja organizacije memorije, interakcije sa procesorima, organizacije razmene između sistemskih uređaja i spoljašnjeg okruženja itd.

Najtipičnije faze projektovanja i razvoja MPS-a su: formalizacija sistemskih zahteva; razvoj strukture i arhitekture IPS-a; razvoj i proizvodnja sistemskog hardvera i softvera; sveobuhvatno otklanjanje grešaka i testiranje prihvatljivosti.

Proces dizajna je iterativni proces. Neispravnosti otkrivene tokom faze prihvatnog testiranja mogu dovesti do korekcije specifikacije, a samim tim i do početka projektovanja čitavog sistema. Greške se moraju otkriti što je prije moguće; Da biste to učinili, potrebno je kontrolirati ispravnost projekta u svakoj fazi razvoja. Postoje sljedeće metode za praćenje ispravnosti projekta: verifikacija (formalne metode dokazivanja ispravnosti projekta); modeliranje; testiranje.

Nedavno se pojavilo dosta posla na verifikaciji softvera, firmvera i hardvera. Međutim, ovi radovi su i dalje teorijske prirode. Stoga se u praksi češće koristi modeliranje ponašanja objekta i testiranje na različitim nivoima apstraktne reprezentacije sistema.

U fazi formalizacije sistemskih zahtjeva posebno je potrebno praćenje ispravnosti projekta, jer mnogi ciljevi dizajna nisu formalizirani ili se u principu ne mogu formalizirati. Funkcionalna specifikacija može biti pregledana od strane tima stručnjaka ili simulirana i testirana kako bi se utvrdilo da li su željeni ciljevi postignuti. Nakon što je funkcionalna specifikacija odobrena, razvoj testnih programa počinje da se utvrđuje da sistem radi ispravno u skladu sa svojom specifikacijom. U idealnom slučaju, razvijeni su testovi koji su u potpunosti zasnovani na ovoj specifikaciji i koji testiraju svaku implementaciju sistema za koju se tvrdi da je sposobna da obavlja funkcije navedene u specifikaciji. Ova metoda je sušta suprotna od ostalih, gdje se testovi grade u odnosu na specifične implementacije. Međutim, u praksi se razvoju testova često daje niži prioritet od projekta, tako da se testni programi pojavljuju dosta nakon što je projekat završen.

Sigurnosna pitanja

1. Objasniti koncepte modularnosti, kanala i mikroprogramabilnosti MPS-a tokom projektovanja.

2. Navedite zadatke koje programeri rješavaju prilikom dizajniranja MPS-a.

3. Navedite glavne faze projektovanja MPS-a.

4. Navedite konceptualne nivoe opisa MPS-a tokom projektovanja i razvoja.

5. Navedite glavne metode za praćenje ispravnosti dizajna MPS-a.

6. Koja svojstva treba da ima dizajnirani MPS da završi fazu otklanjanja grešaka?

7. Navedite vrste kvarova prilikom projektovanja MPS-a.

8. Navedite uzroke fizičkih i subjektivnih kvarova MPS-a.

9. Objasnite pojmove: dijagnoza greške, otklanjanje grešaka.

Ministarstvo nauke i obrazovanja Republike Kazahstan

Multidisciplinary College

Državni univerzitet Sjevernog Kazahstana

nazvan po akademiku M. Kozybaevu

Objašnjenje

za projekat kursa

u disciplini: “Digitalni uređaji i mikroprocesorski sistemi”

na temu: „Projektovanje mikroprocesorskog sistema baziranog na mikroprocesoru I 8086“

Opcija br. 16

Završio: student gr. RES-k-09

Safronov S.V.

Provjerio: nastavnik

Mihailova A.N.

Petropavlovsk 2010

1. Uvod

2. Opšta struktura Ministarstva željeznica

3. 16-bitni i8086 mikroprocesor

3.1 Komandni sistem

4.Unutrašnja struktura

5. Memorijski uređaji

6. RAM. Principi konstrukcije

7. Memorija samo za čitanje (ROM)

8.Digitalno-analogni pretvarači (DAC)

9.Izrada funkcionalnog dijagrama ulazno/izlaznog modula

10 Zaključak

Reference

Dodatak A

1. Uvod

Svrha discipline „Digitalni uređaji i mikroprocesori“ je proučavanje principa konstruisanja digitalnih uređaja različite funkcionalne složenosti – od logičkih elemenata do mikroprocesora i mikroračunara.

Kompaktna mikroelektronska „memorija“ se široko koristi u modernoj elektronskoj opremi za različite namene. U PC-u, memorija je definirana kao funkcionalni dio dizajniran za snimanje, pohranjivanje i izdavanje naredbi i obrađenih podataka. Skup tehničkih sredstava koja implementiraju memorijsku funkciju naziva se uređaj za pohranu (storage device). Da bi se osigurao rad procesora (mikroprocesora) potreban je program, odnosno niz naredbi i podataka na kojima procesor izvodi operacije propisane komandama. Komande i podaci ulaze u glavnu memoriju računara putem ulaznog uređaja, na čijem izlazu dobijaju digitalni oblik reprezentacije, odnosno oblik kodnih kombinacija O i 1. Glavna memorija se po pravilu sastoji od dva vrste memorije: operativna (RAM) i stalna (ROM).

RAM je dizajniran za pohranjivanje promjenjivih informacija i omogućava da se njegov sadržaj mijenja dok procesor izvodi računske operacije s podacima. To znači da procesor može odabrati (režim čitanja) instrukcijski kod i podatke iz RAM-a i, nakon obrade, smjestiti rezultirajući rezultat u RAM (režim pisanja).

Ovaj kurs je posvećen proučavanju memorijskog bloka. Naime, zadatak je izgraditi memorijski prostor zadane veličine i konfiguracije.

2. Opšta struktura Ministarstva željeznica

Mikroprocesor (MP) - centralni dio svakog mikroprocesorskog sistema (MPS) - uključuje aritmetičko-logičku jedinicu (ALU) i centralnu upravljačku jedinicu (CCU), koja implementira komandni ciklus. MP može funkcionirati samo kao dio MPS-a, koji uključuje, pored MP-a, memoriju, ulazno/izlazne uređaje, pomoćna kola (generator takta, kontrolere prekida i direktni pristup memoriji (DAM), upravljačke programe sabirnice, registre za zaključavanje, itd. .

U bilo kojem MPS-u mogu se razlikovati sljedeći glavni dijelovi (podsistemi):

eksterni uređaji (eksterna memorija + uređaji za ulaz/izlaz);

podsistem prekida;

podsistem direktnog pristupa memoriji.

procesorski modul;

Slika 1 – Struktura MPS-a sa interfejsom “Common Bus”.

Komunikacija između procesora i drugih MPS uređaja može se vršiti korištenjem principa radijalnih veza, zajedničke magistrale ili kombinirane metode. U jednoprocesorskim MPS-ovima, posebno 8- i 16-bitnim, najviše je rasprostranjen komunikacioni princip “Common Bus” u kojem su svi uređaji povezani na interfejs na isti način (slika 1).

Svi signali interfejsa su podeljeni u tri glavne grupe - podaci, adresa i kontrola. Brojni tipovi sučelja "Common Bus" omogućavaju prijenos preko zasebnih ili multipleksiranih linija (sabirnica). Na primjer, Microbus sučelje, na kojem radi većina 8-bitnih MPU-ova baziranih na i8080, prenosi adresu i podatke na odvojenim magistralama, ali neki kontrolni signali se prenose na sabirnici podataka. Q-bus interfejs koji se koristi u mikroračunarima iz DEC-a (domaći analogni - mikroprocesori serije K1801) ima multipleksiranu magistralu adresa/podataka, preko koje se ove informacije prenose sa vremenskom podjelom. Naravno, ako postoji multipleksirana magistrala, potrebno je u upravljačke linije uključiti poseban signal koji identifikuje vrstu informacija na sabirnici. Informacije se razmjenjuju preko sučelja između dva uređaja, od kojih je jedan aktivan, a drugi pasivan. Aktivni uređaj generiše pasivne adrese uređaja i kontrolne signale. Aktivni uređaj je obično procesor, a pasivni uređaj je uvijek memorija i neki računari.

Međutim, ponekad host uređaji velike brzine mogu djelovati kao glavni (aktivni uređaji) na sučelju, kontrolirajući razmjenu s memorijom. Koncept “Common Bus” pretpostavlja da se pristup svim MPS uređajima vrši u jednom adresnom prostoru, međutim, kako bi se proširio broj adresabilnih objekata, u nekim sistemima adresni prostori memorije i memorije, a ponekad čak i programske memorije i memorija podataka, su umjetno odvojeni.

3.16-bitni i8086 mikroprocesor

Intel je 1978. godine objavio prvi 16-bitni procesor i8086. Frekvencija - 5 MHz, performanse - 0,33 MIPS za instrukcije sa 16-bitnim operandima (kasnije su se pojavili procesori od 8 i 10 MHz). Tehnologija od 3 mikrona, 29.000 tranzistora. Adresabilna memorija 1 MB. Godinu dana kasnije pojavio se i8088 - isti procesor, ali sa 8-bitnom magistralom podataka. Istorija IBM PC-a je počela sa njim, neraskidivo povezana sa svim daljim razvojem Intelovih procesora. Masovna distribucija i otvorenost IBM PC arhitekture dovela je do lavinskog tempa pojave novog softvera koji su razvili veliki, srednji i mali. firmama, kao i pojedinačnim entuzijastima. Tehnički napredak tada i sada bio bi nezamisliv bez razvoja procesora, ali, uzimajući u obzir ogroman obim već postojećeg softvera za računare, i tada se pojavio princip kompatibilnosti softvera unazad - stari programi bi trebali raditi na novim procesorima. Dakle, sve inovacije u arhitekturi narednih procesora morale su biti vezane za postojeće jezgro.

16-bitni MP i8086 bio je dalji razvoj linije MP-a sa jednim čipom koju je započeo i8080. Uz povećanje bitnog kapaciteta, i8086 implementira niz novih arhitektonskih rješenja:

proširen je komandni sistem (skupom operacija i metoda adresiranja);

MP arhitektura je fokusirana na višeprocesorski rad. Grupa pomoćnih LSI (kontrolera i specijalizovanih procesora) je razvijena za organizovanje multimikroprocesorskih sistema različitih konfiguracija;

počelo je kretanje ka kombinovanju izvođenja različitih operacija u vremenu. MP uključuje dva paralelna radna uređaja

obrada podataka i komunikacija sa autoputem, što omogućava vremensko kombinovanje procesa obrade informacija i njihovog prenošenja duž autoputa;

uvedena je nova (u poređenju sa i8080) organizacija memorije, koja je kasnije korišćena u svim starijim modelima INTEL porodice – segmentacija memorije. Da bi se održao kontinuitet modela sa i8080, i8086 pruža dva režima rada - „minimalni“ i „maksimalni“, au minimalnom režimu i8086 jednostavno radi kao prilično brz 16-bitni i8080 sa proširenim komandnim sistemom ( arhitektura MPS-a zasnovanog na i8086-min liči na arhitekturu na bazi i8080).

Maksimalni režim je usmeren na rad i8086 kao dela multimikroprocesorskih sistema, u kojima, pored nekoliko centralnih procesora i8086, mogu funkcionisati specijalizovani i8089 ulazno/izlazni procesori i i8087 plutajući aritmetički koprocesori. Hajde da jasnije definišemo pojmove uvedene gore:

Centralni procesor - održava sopstveni ciklus komandi, izvršava program pohranjen u sistemskoj memoriji nakon resetovanja sistema, kontrola se obično prenosi na centralni procesor (ili jedan od CPU-a, ako ih ima nekoliko u sistemu); Specijalizovani procesor - održava sopstveni ciklus instrukcija, izvršava program pohranjen u sistemskoj memoriji, ali se inicijalizira samo naredbom iz CPU-a i po završetku programa obavještava CPU da je završio svoj rad. Koprocesor ne podržava sopstveni ciklus instrukcija, on izvršava komande koje je za njega izabrao CPU iz opšteg toka komandi. U suštini, koprocesor je proširenje CPU-a.

3.1 Komandni sistem

U sistemu instrukcija mikroprocesora 8086 bilo je 98 instrukcija: 19 komandi za prenos podataka, 38 komandi za obradu podataka, 24 različite uslovne i bezuslovne komande grananja i 17 komandi za upravljanje procesorom.

Svaka instrukcija se sastojala od koda operacije (nazvanog opcode) i operanada. Tipično, operacijski kod je dodijeljen prvom bajtu naredbe i tri srednja bita drugog bajta, ili (u slučaju jednobajtne komande) visokom dijelu prvog bajta naredbe. Ukupno, postoji skoro 4000 različitih komandnih opcija u i8086.

Prema svojoj namjeni, mikroprocesorske komande I8086 podijeljene su u 6 grupa:

1 Komande za prijenos podataka: MOV, XCHG, PUSH, POP, PUSHF, POPF, LEA, LDS, LES, LAHF, SAHF, XLAT, IN.

2 Aritmetičke komande: ADD, ADC, INC, AAA, DAA, SUB, SBB, DEC, NEG, CMP, AAS, DAS, MUL, IMUL, DIV, IDIV, AAM, AAD.

3 logičke komande: NOT,SHL / SAL,SHR,SAR,ROL,ROR,RCL,RCR,

I, TESTIRAJ, ILI, XOR.

4 lančane naredbe za manipulaciju: CMPS, LODS, MOVS, REP, SCAS, STOS.

5 komandi za prijenos kontrola: JMP, CALL, RET, LOOP/LOOPE, LOOPZ, LOOPNE/LOOPNZ, JCXZ, JE/JZ, JNE/JNZ, JL/JNGE, JLE/JNG, JB/JNAE, JBE/JNA, JP/JPE , JNP/JPO, JO, JNO, JS, JNS, JG/JNLE, JGE/JNL, JA/JNBE, JAE/JNB.

6 komandi za kontrolu procesora: CLC, CMC, STC, CDL, STD, CLI, HLT WAIT, ESC, LOCK

4.Unutrašnja struktura

Blok dijagram i8086 MP prikazan je na Sl. MP uključuje tri glavna uređaja:

UOD - uređaj za obradu podataka;

USM - uređaj za komunikaciju sa autoputem;

UUS - uređaj za kontrolu i sinhronizaciju.

UOD je dizajniran za izvršavanje instrukcija i uključuje 16-bitni ALU, sistemske registre i druga pomoćna kola; registarski blok (RON, osnovni i indeksni) i mikroprogramski kontrolni blok.

USM osigurava formiranje 20-bitne fizičke memorijske adrese i 16-bitne adrese domaćina, izbor komandi iz memorije, razmjenu podataka sa memorijom, hostom i drugim procesorima preko magistrale. USM uključuje sabirač adresa, blok registara reda komandi i blok registara segmenta.

UUS obezbeđuje sinhronizaciju rada MP uređaja, generisanje kontrolnih signala i statusnih signala za razmenu sa drugim uređajima, analizu i odgovarajući odgovor na signale drugih MPS uređaja.

MP može raditi u jednom od dva načina rada - “minimum” (min) i “maksimum” (max). Minimalni režim je dizajniran za implementaciju jednoprocesorske MPS konfiguracije sa organizacijom sličnom MPS-u zasnovanom na i8080, ali sa povećanim adresnim prostorom, većom brzinom i značajno proširenim sistemom instrukcija. Maksimalna konfiguracija pretpostavlja prisustvo nekoliko MP-a i posebne jedinice bus arbitra u sistemu (koristi se Multibus interfejs).

Eksterni pinovi MP i8086 široko koriste princip multipleksiranja signala - prenos različitih signala preko zajedničkih linija sa vremenskom podelom. Osim toga, isti pinovi se mogu koristiti za prijenos različitih signala u zavisnosti od načina rada (min - max).hardverski dizajn... implementiran kursni projekat mikroprocesor sistem on baza mikrokontrolera - ... rad uređaja On osnovu funkcije uređaja...

Dizajn mikroprocesor uređaji za obradu podataka

Ostalo >> Računarstvo, programiranjeKurs dizajn je sistem prikupljanje i obrada podataka, implementirano on osnovu moderna elementna baza - mikroprocesor ... on osnovu drugi MP je sličan, iako ima neke karakteristike povezane sa razlikama u arhitekturi mikroprocesori ...

Mikroprocesor sistemima

Izvještaj o praksi >> InformatikaPrema obrazovnoj praksi" Mikroprocesor sistemi" Opcija br. 1 Izvršeno... Računar za automat dizajn, naučna istraživanja, ... ko treba da zna osnove organizacija i funkcionisanje univerzalnog... kursor udesno on jedna pozicija. On simbol...

Periferni hardver i softver sistemima prikupljanje očitavanja toplomjera

Sažetak >> RačunarstvoUporedivo sa 16-bitnim mikroprocesori i mikrokontroleri za performanse i... računarstvo Za dizajn on osnovu pouzdani računari... način izrade lemljenja mikroprocesor sistemima on osnovu AVR je akvizicija...